Categories

{{ selectedCategory.name }}

Infineon Aurix: How to find two or more problematic functions in a wider range if AGBT FIFO has overflowed?

Error message AGBT FIFO overflow indicates that TriCore’s internal FIFO overflowed, which means that in a short period of time too many trace messages were written into FIFO.

Below steps explain on the TC3xx example how to define custom triggers and use an algorithmic approach to find two or more problematic functions that generate too many trace messages in a wider range.

To find a problematic function in a narrow range refer to this topic.

Possible solutions

In the Disassembly Window you found the problematic functions, but the range is too wide. It spans between 0x10 - 0x60. You have to divide it into two or more narrower ranges.

1. Define a custom trigger.

To exclude the range between 0x10 - 0x60 from tracing, follow the below steps. To visualize it refer to this topic.

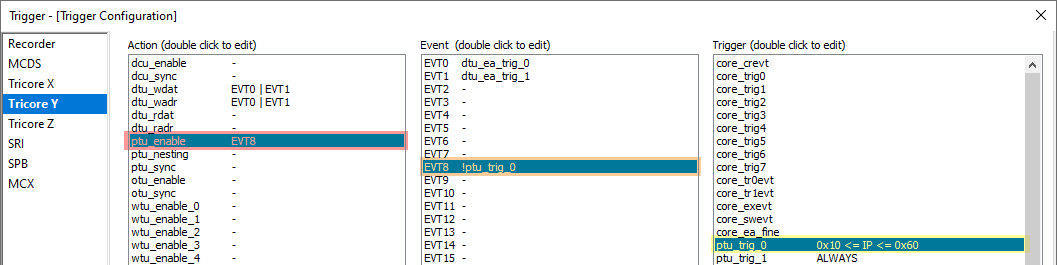

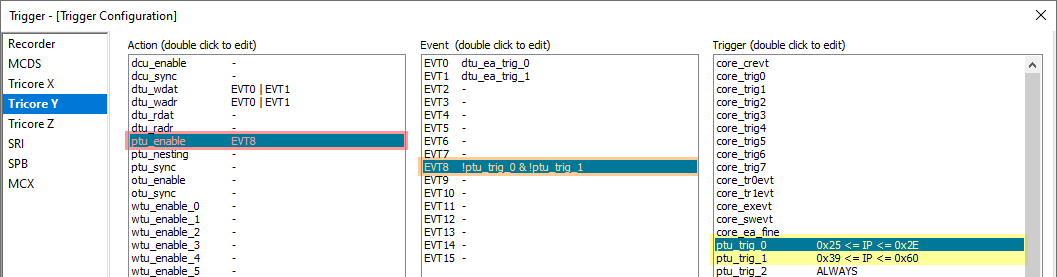

1. Open Manual Hardware Trigger / TriCore Y. Refer to winIDEA Help for more information about manual configuration.

2. Set ptu_trig_0 to 0x10 <= IP <= 0x60 in the Trigger section.

3. Set EVT8 to !ptu_trig_0 in the Event section.

4. Set ptu_enable to EVT8 in the Action section.

2. Half the range between 0x10 - 0x60.

1. Take the range between 0x10 - 0x60 and divide it into two ranges, each a half of the original size:

- 0x10 - 0x38

- 0x39 - 0x60

To visualize it refer to this topic.

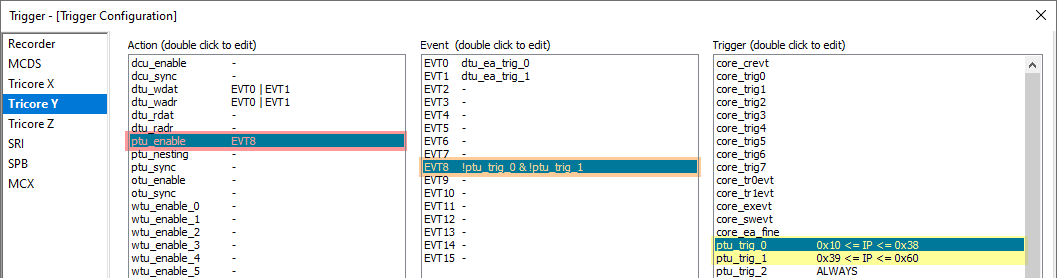

2. Define a custom trigger and set:

- ptu_trig_0 to 0x10 <= IP <= 0x38

- ptu_trig_1 to 0x39 <= IP <= 0x60 in the Trigger section.

3. Set EVT8 to !ptu_trig_0 & !ptu_trig_1 in the Event section.

4. Make sure ptu_enable is set to EVT8 in the Action section.

3. Half the first range between 0x10 - 0x38 and test it.

It is assumed that the second range between 0x39 - 0x60 is fixed.

3.1. Take the first range between 0x10 and 0x38, that is 0x10 - 0x24. To visualize it refer to this topic.

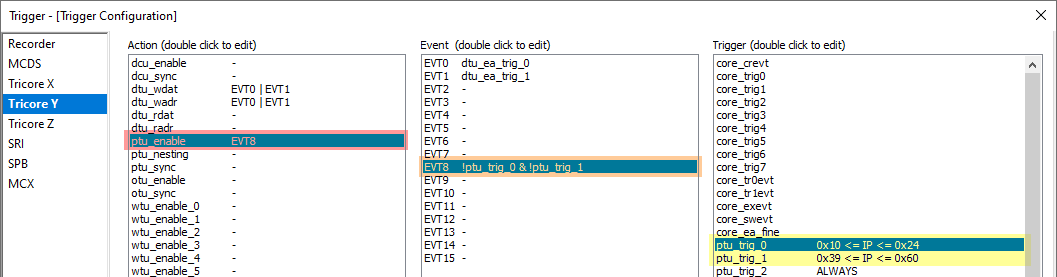

a. Define a custom trigger and set:

- ptu_trig_0 to 0x10 <= IP <= 0x24

- ptu_trig_1 to 0x39 <= IP <= 0x60 in the Trigger section.

b. Set EVT8 to !ptu_trig_0 & !ptu_trig_1 in the Event section.

c. Make sure ptu_enable is set to EVT8 in the Action section.

d. Run the Analyzer. Error message AGBT FIFO overflow is displayed which means that the problematic function is not in the range defined by the EVT8 event.

3.2. Take the first range between 0x10 and 0x38, that is 0x25 - 0x38. To visualize it refer to this topic.

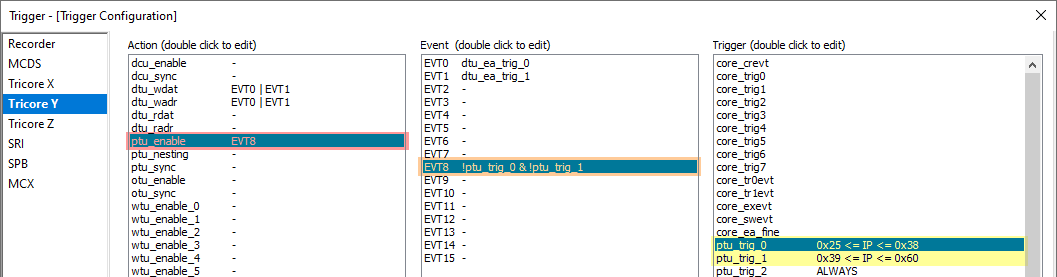

a. Define a custom trigger and set:

- ptu_trig_0 to 0x25 <= IP <= 0x38

- ptu_trig_1 to 0x39 <= IP <= 0x60 in the Trigger section.

b. Set EVT8 to !ptu_trig_0 & !ptu_trig_1 in the Event section.

c. Make sure ptu_enable is set to EVT8 in the Action section.

d. Run the Analyzer. Error message AGBT FIFO overflow is not displayed.

3.3. Half the range further. To visualize it refer to this topic.

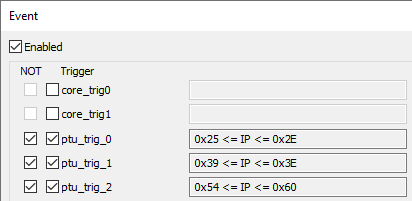

a. Define a custom trigger and set:

- ptu_trig_0 to 0x25 <= IP <= 0x2E

- ptu_trig_1 to 0x39 <= IP <= 0x60 in the Trigger section.

b. Set EVT8 to !ptu_trig_0 & !ptu_trig_1 in the Event section.

c. Make sure ptu_enable is set to EVT8 in the Action section.

d. Run the Analyzer. Error message AGBT FIFO overflow is not displayed.

By dividing the range even further does not yield positive results, meaning you have found the minimum range for the first part.

3. Half the second range between 0x39 - 0x60 and test it.

Repeat the above procedure of dividing the range for the second part that spans between 0x39 - 0x60, while the first part remains (0x25 - 0x2E) fixed.

If a memory range is again too wide you can use the same algorithm and divide the range again into two parts.

4. Results.

After halving the range until the end you will have 2 memory ranges or 3 ranges with problematic functions which generate error message AGBT FIFO overflow.

The maximum amount of ranges we can specify as hardware resources for Events are limited as Event MUX can have max 3 ptu trigger inputs specified.

Example for this specific use case:

- ptu_trig_0 0x25 <= IP <= 0x2E

- ptu_trig_1 0x39 <= IP <= 0x3E

- ptu_trig_2 0x54 <= IP <= 0x60

Sorry this article didn't answer your question, we'd love to hear how we can improve it.

Note: This form won't submit a case. We'll just use it to make this article better.

Similar topics

{{ topic.Title }} {{ topic.Ddate | formatDate }}

{{ topic.Content }}